一、系统概述

CCS907 企业能源管控平台是分布式平台(本地系统),使用物联网技术,实现企业各处各类能源进行集成管理模式, 对企业的生产、输送、分配和消耗各环节实行动态监控和数据化管理。

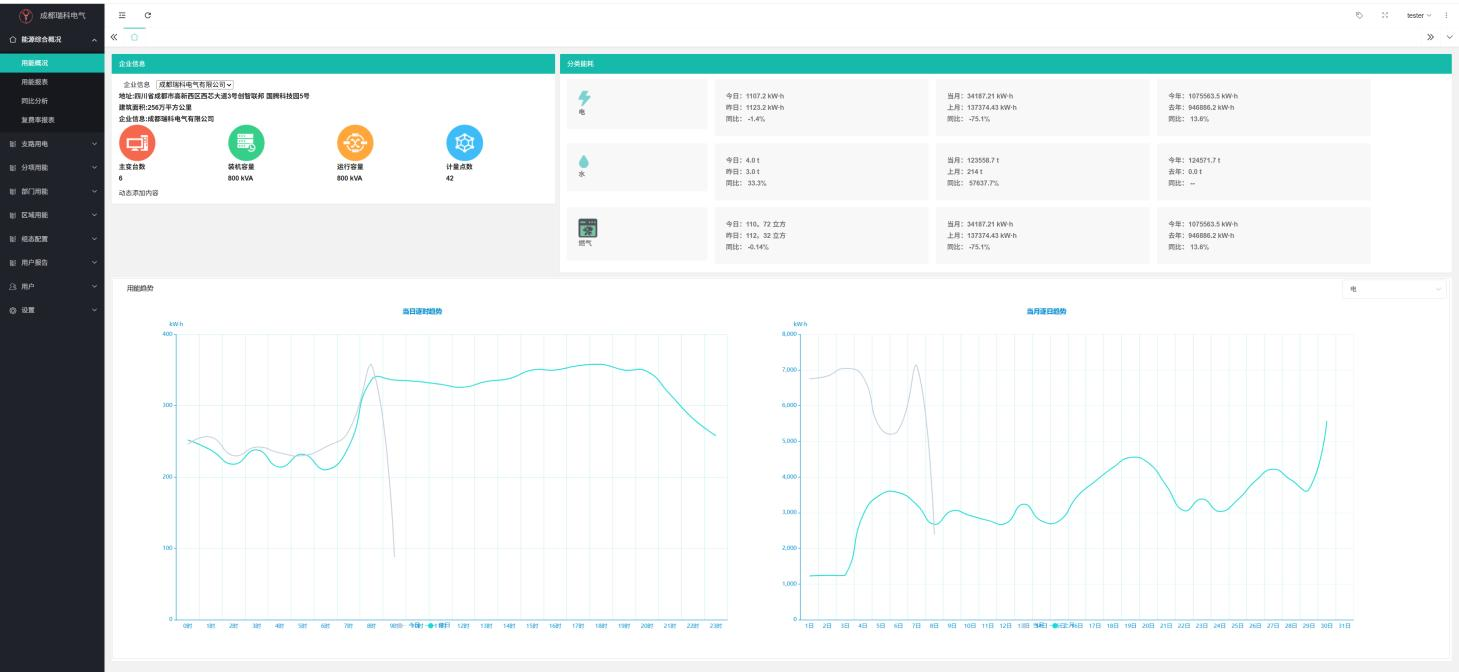

CCS907 企业能源管控平台,监测企业的水、电、燃气、蒸汽及压缩空气等各类能源的消耗情况,通过数据分析,帮 助企业针对各种能源需求及实际用能情况、产品能源单耗、工序能耗、重点设备用能等进行能耗统计、同环比分析、能源 成本分析、用能预测、碳排分析,为企业加强能源管理,提高能源利用效率,以及为节能评估、能源审计提供基础数据。

CCS907Cloud 企业能源管控云平台,是以 CCS907 企业能源管控平台做为企业能源管理的本地系统,连通互联网外网, 接入云空间建成云平台。云平台支持用户端 PC 机、手机 APP 的远程登录、访问与各种操作。

在 CCS907Cloud 企业能源管控云平台上实现的所有功能与 CCS907 企业能源管控平台的本地监控中心相同,方便企业 各级管理人员进行远程监控与管理。

二、适用范围

适用于新建或者改建的能源供给企业、高耗能企业和离散制造企业厂房、工业园区、集团公司等不同企业的能耗监测 管理。 具体工程可结合当地政府部门的要求和企业的管理需求,设计 CCS907 企业能源管控系统的软硬件具体功能与设备配 置,以满足各企业能耗监控的不同要求。

三、系统结构

CCS907Cloud 建筑能耗监测管理系统云平台,采用分布式组网结构。平台系统分为设备感知层(包括第三方子系统)、 网络传输层、中心监控管理层、云端平台层与客户应用层。

3.1 设备感知层

设备感知层通过智能仪表与智能传感器对实时参数进行监测和计量,设备感知层作为云平台的基础数据来源。建筑能 耗监测管理系统可方便接入第三方子系统,做为系统的综合数据来源。

3.2 网络传输层

网络传输层通过强大的通讯协议转换功能,将采集到的设备感知层的数据传递到本地监控中心及云端平台层,起到承上 启下的作用。

3.3 本地监控中心管理层

企业能源管控平台可以在企业本地设置监控中心,方便建筑物现场的监测与管理。也可以直接上传云平台。

3.4 云端平台层与云端客户应用层

云平台采用云计算技术架构,由云数据服务器、云Web服务器等多个服务器组成,完成实时的数据采集、数据存储、 数据计算与数据分析,并通过Web服务器提云端供客户应用。 云端应用层是面向客户端,给客户端PC、移动PC、手机APP等智能终端提供远程登录访问、监视、控制、能效管理与设备运维等云端应用服务。云端应用层采用最新的H5和APP技术,跨平台通过客户端浏览器和移动APP即可访问平台, 不需要再单独安装客户端软件。

3.5 CCS907Cloud企业能源管控云平台结构示意图

四、系统功能

4.1 三维展示

通过 3D 建模,三维立体展示企业及各区域的各类能耗位置、数据指标、异常情况、通讯情况,以及展示当月分类能 耗统计、当年与去年用电量对比、分类能耗点对比等信息。 通过对动力管线虚拟仿真,展示设备的实时运行状态及能源消耗情况,结合动态的能源流向,为企业提供身临其境的 直观体验。

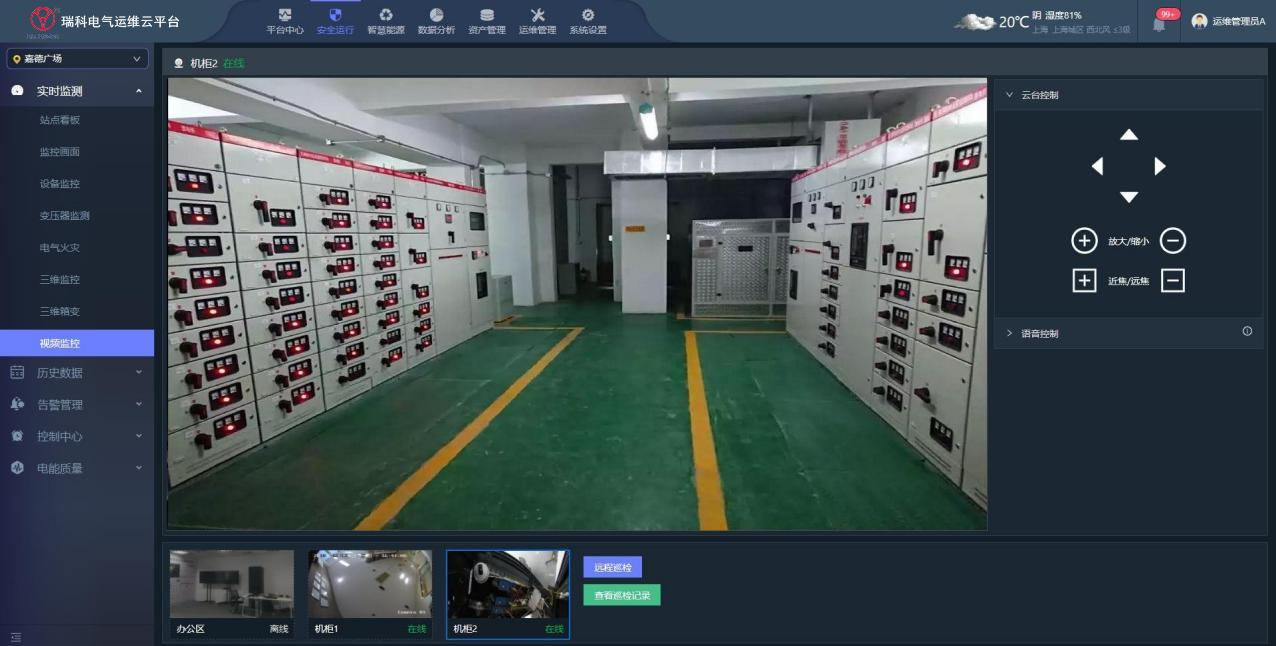

4.2 视频监控

支持视频实时监控,可远程视频、语音指导现场操作。可实现告警、视频联动。

4.3 主菜单画面

层示企业的用电情况(,包括变压器与当日用电峰谷平用电概况)、日/月/年分类能耗前数据、当年/去年能耗同比分析、 当年能耗趋势,以及用户侧重的各类能耗数据统计。

4.4 单位产值能耗统计

能耗监测管理系统与企业 MES 系统对接,导入 MES 系统的产品产量与产值。若不能直接自动导入的各类数据提供手工 录入。 通过系统采集到的各类能耗数据,结合企业的产品产量与产值,统计单位产品产值能耗。

4.5 能源集中管控(大屏展示)

系统将所有能源数据集成在一个菜单看板上,进行大屏展示,从多个角度对比分析,完成各条生产线的能耗数据对比, 让用户全面掌握整个企业的能源消耗、能源成本、碳排放等各能耗指标。

4.6 绩效考核

针对各条生产线、各车间、各班组设置生产考核指标与评分标准,结合单位能耗数据,进行能源绩效考核,科学量化 考核对象的用能差距,有针对性的提高用能效率。

4.7 设备运行管理

系统对各个能耗设备进行实时数据采集,监测能耗设备的开机运行、停机、待机及异常状况,对温度、湿度、流量、 压力、速度等生产线工艺的数据进行实时监测。

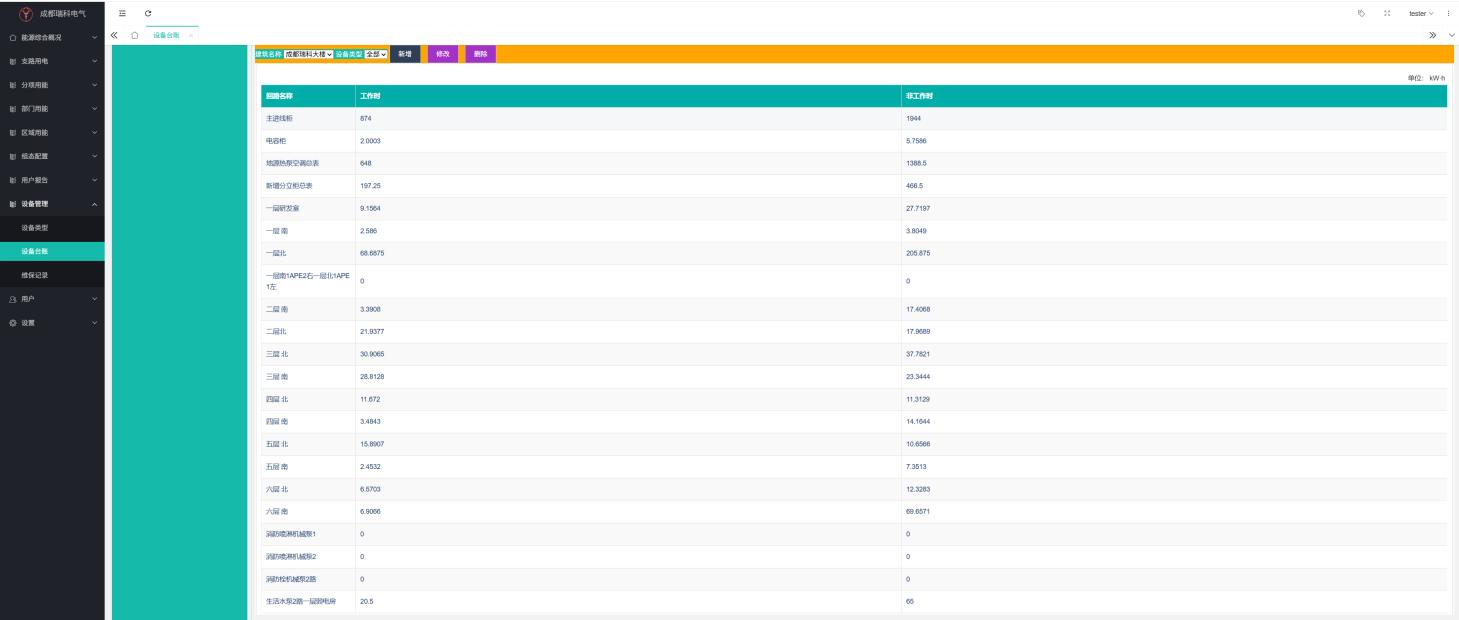

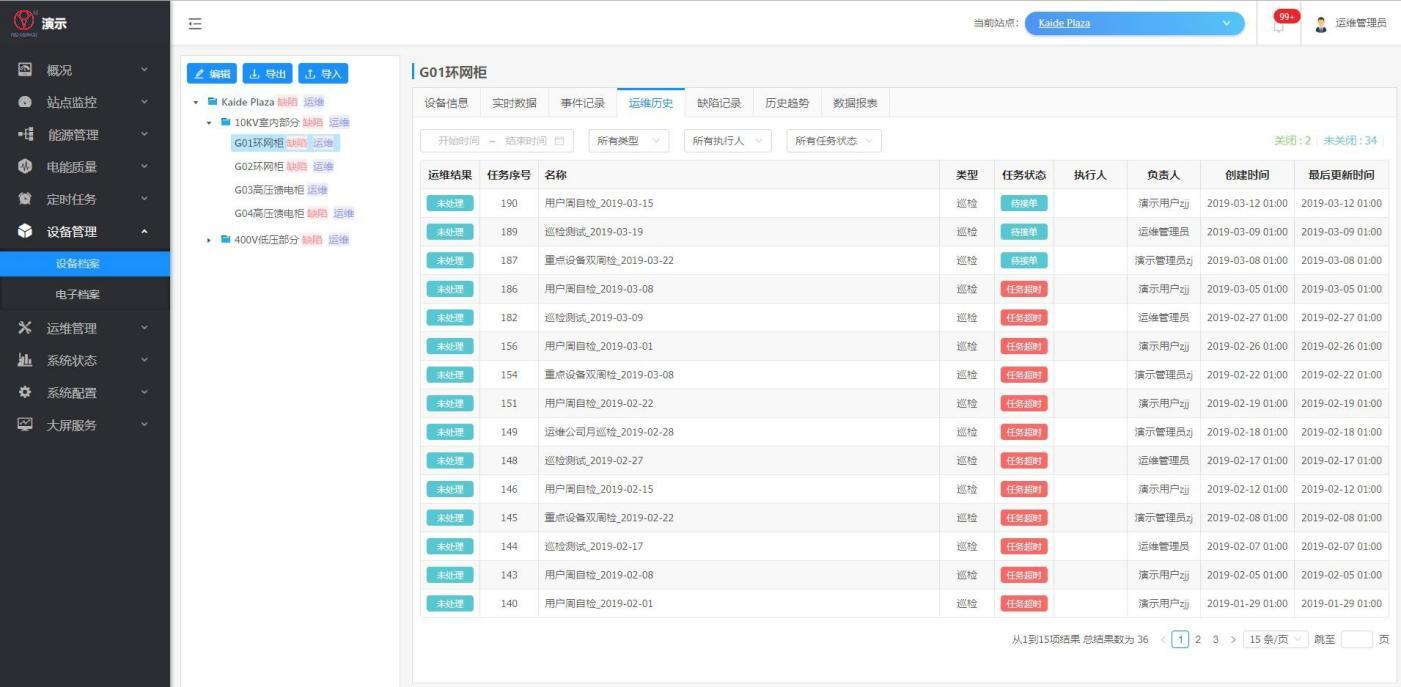

4.8 数字资产管理与电子档案

分类能源的用能设备图纸、检测试验报告等电子材料可上传到云平台上进行管理。所有现场设备的产品信息、使用 手册、告警和故障记录、检修维修记录等都在云平台上管理纪录。以上所有电子资料和信息都可以在 APP 上在线查看。

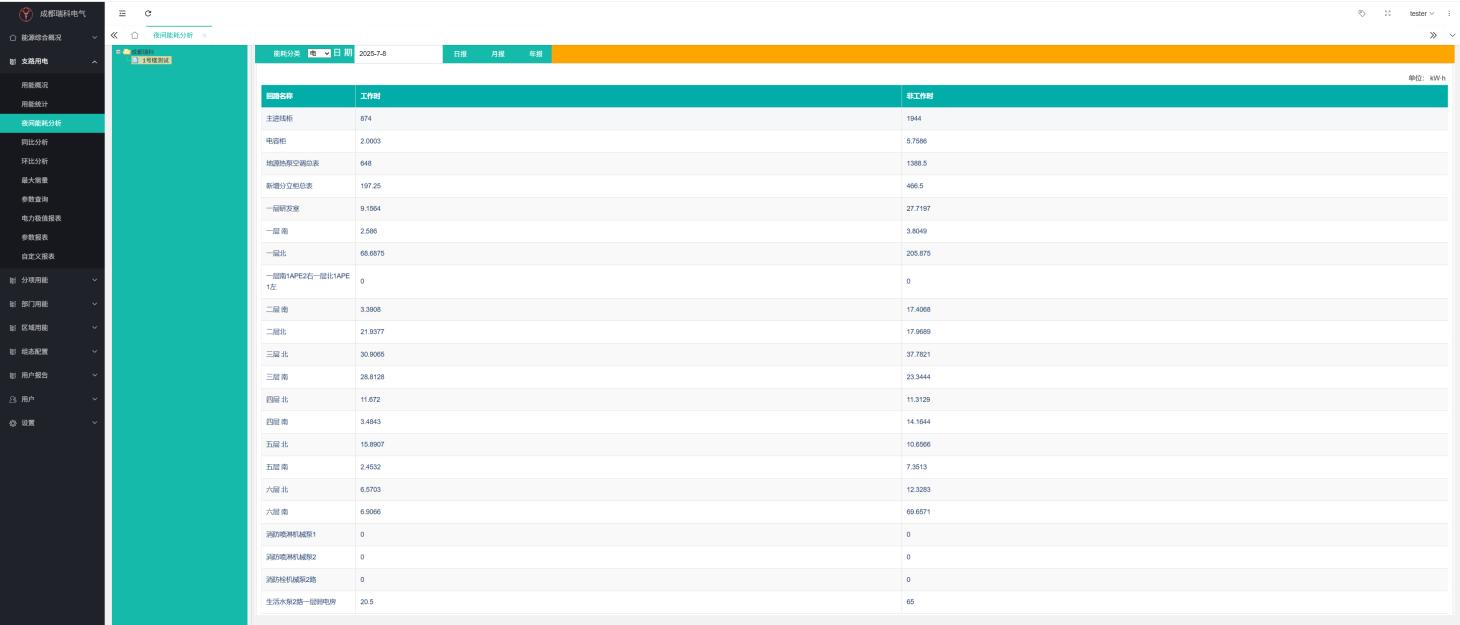

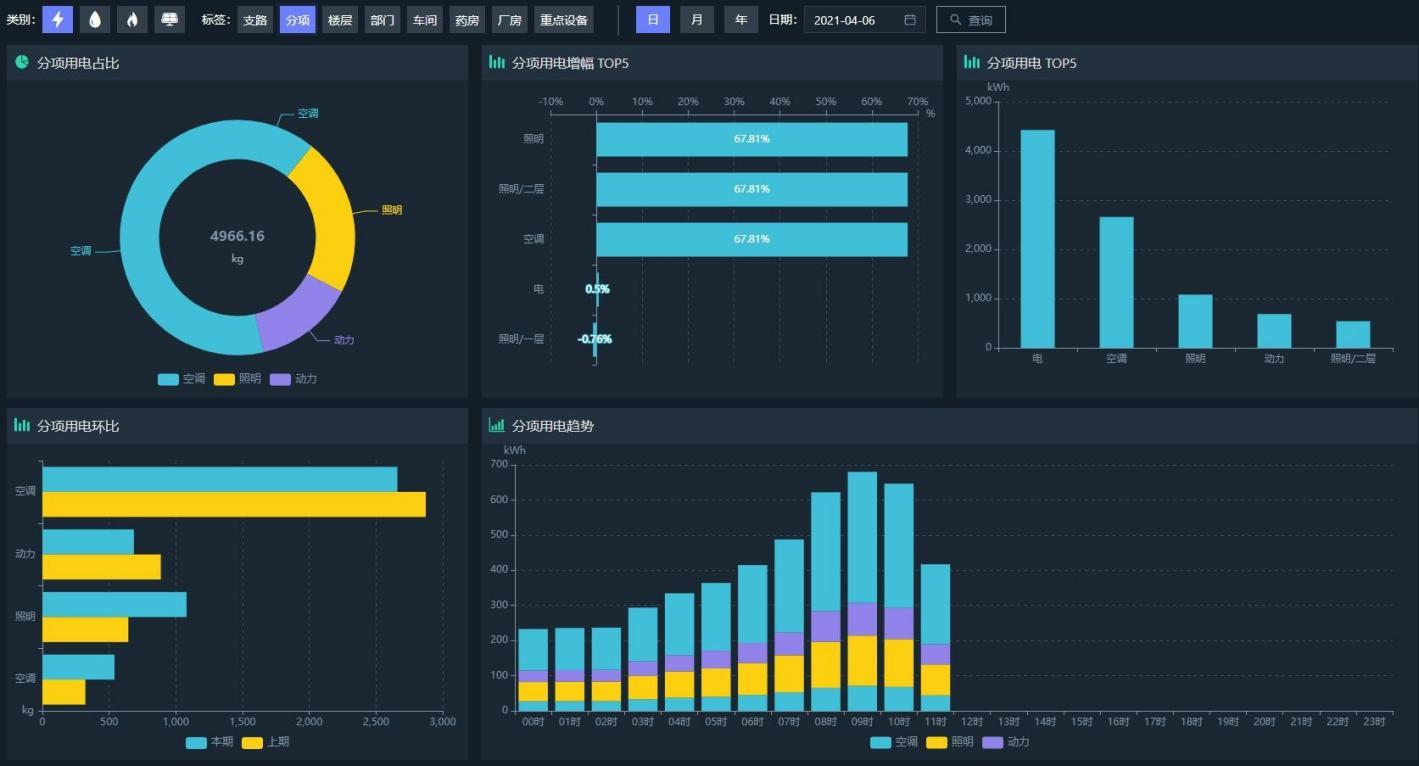

4.9 能耗分析管理

系统提供水、电、气等能源在输送、转换、使用各环节的能耗分析,让企业能及时发现异常用能情况,及时纠正能源 的滴漏、跑、冒等能源浪费现象。

4.10 能效分析报告

系统提供设备能效监测数据与分析结果,以及节能建议,让企业管理人员了解整个企业的能效水平,制定节能措施。 让系统为企业节能降耗提供数据支持。

4.11 能源管网组态(工业组态)

用户自定义监控管网,通过友好人机界面展示监测数据,支持远程控制设备。

4.12 手机 APP

通过手机 APP,可以远程登录、访向、操作系统。在手机 APP 上可直接完成登下功能:

电气一次接线图及水、气管网图查看

水、电、气各类能源数据查看

各类能源消耗统计与分析

视频监视与回放

运行环境巡视

运维任务执行

五、设备选型

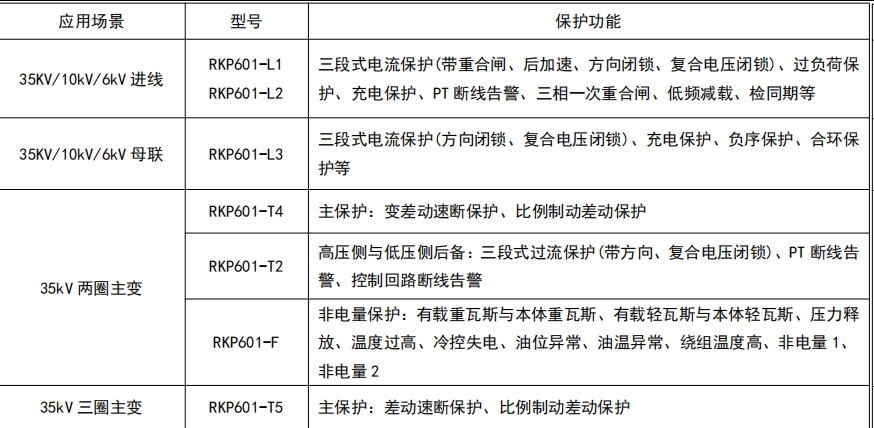

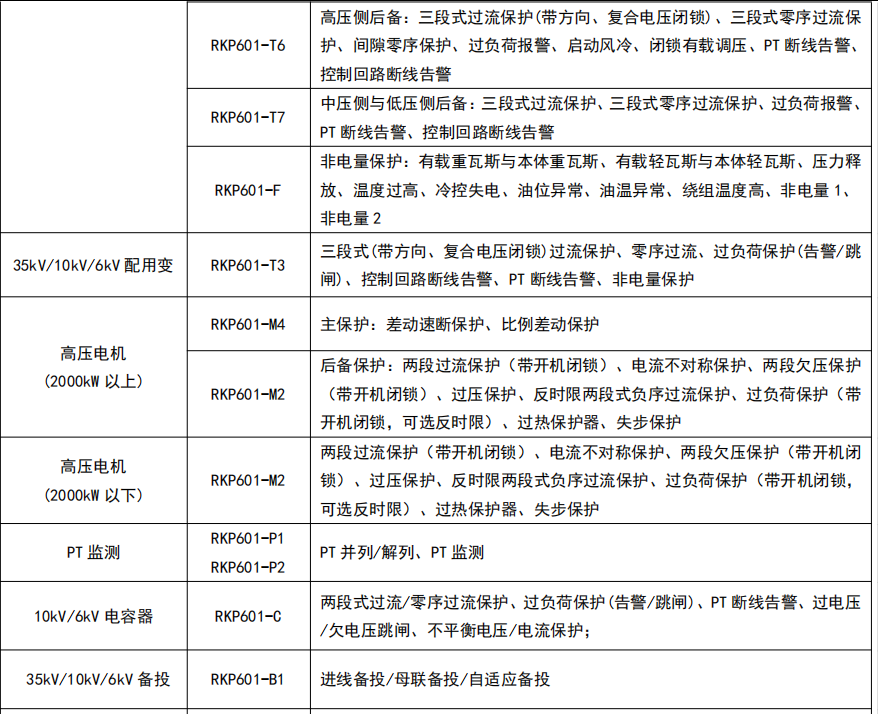

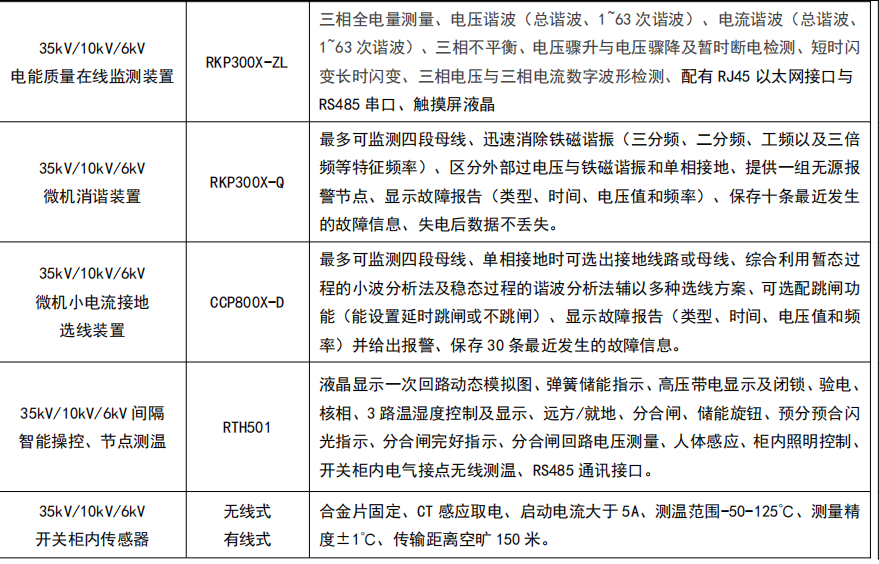

5.1 高压配电设备

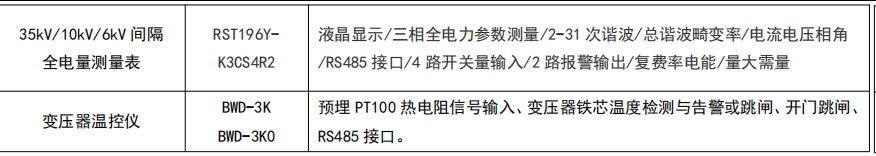

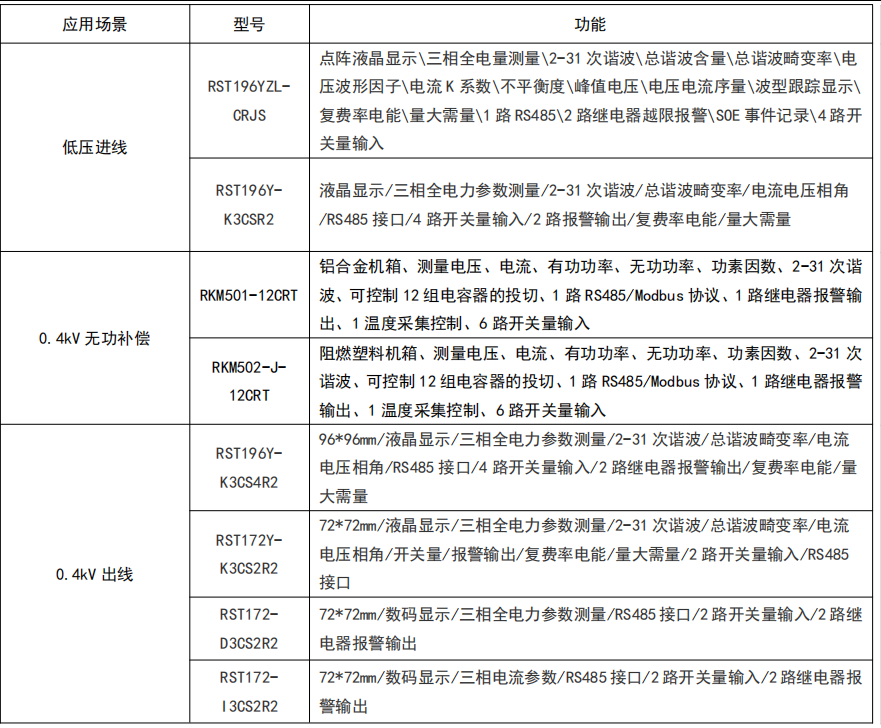

5.2 低压配电设备

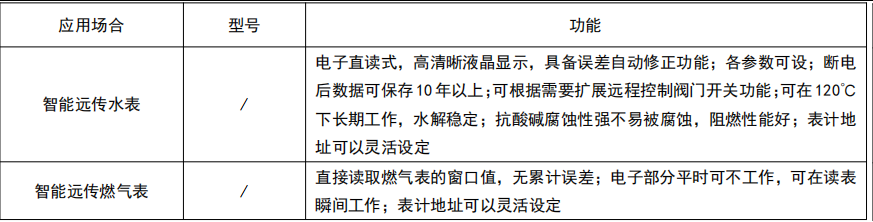

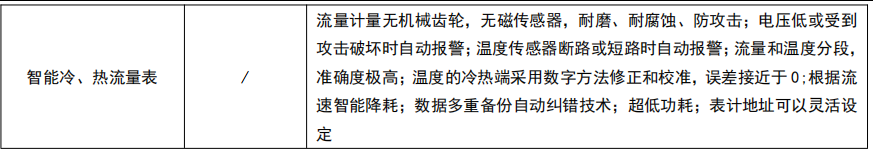

5.3 智能流量表计

5.4 其他设备

Copyright 2018 四川臻诚电气有限公司 版权所有 网站建设:三以网络 备案号:蜀ICP备2020034396号-1